NASA đang lên kế hoạch cho một dự án bộ xử lý mới để trang bị cho các máy tính sẽ bay ra ngoài vũ trụ trong tương lai. Có tên gọi High-Performance Spaceflight Computing (HPSC), dự án này được NASA hứa hẹn sẽ mang lại khả năng tính toán nhanh hơn "ít nhất 100 lần" so với các máy tính hiện nay trên tàu vũ trụ – vốn được phát triển từ gần 30 năm trước.

Đáng chú ý, thay vì lựa chọn các kiến trúc CPU thường thấy như x86 của Intel hay ARM, lần này bộ xử lý được NASA lựa chọn dùng kiến trúc RISC-V, một kiến trúc CPU vẫn còn lạ lẫm với hầu hết người dùng trên thế giới để trang bị cho các tàu không gian của mình. Bộ xử lý này sẽ là sự hợp tác giữa hai công ty SiFive và Microchip.

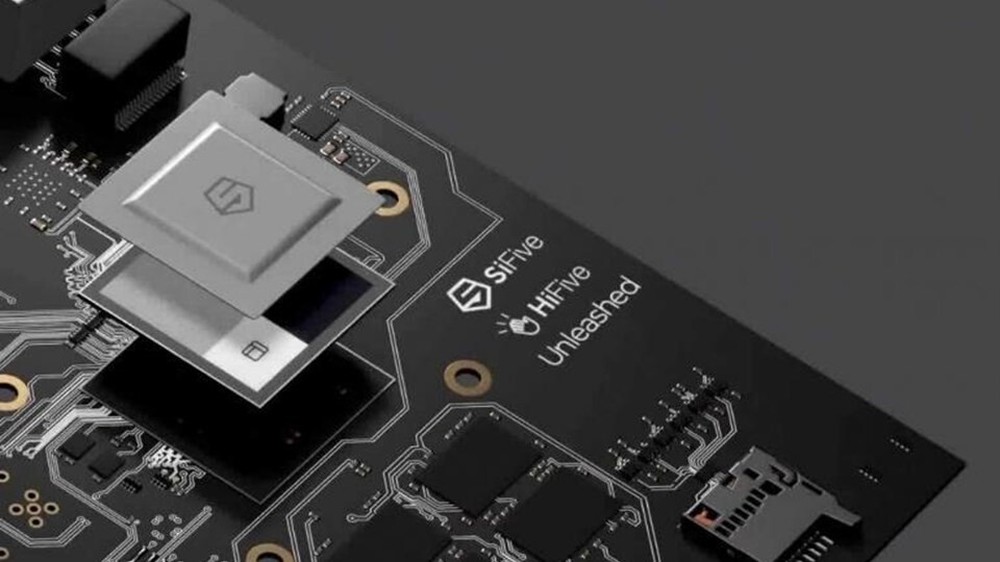

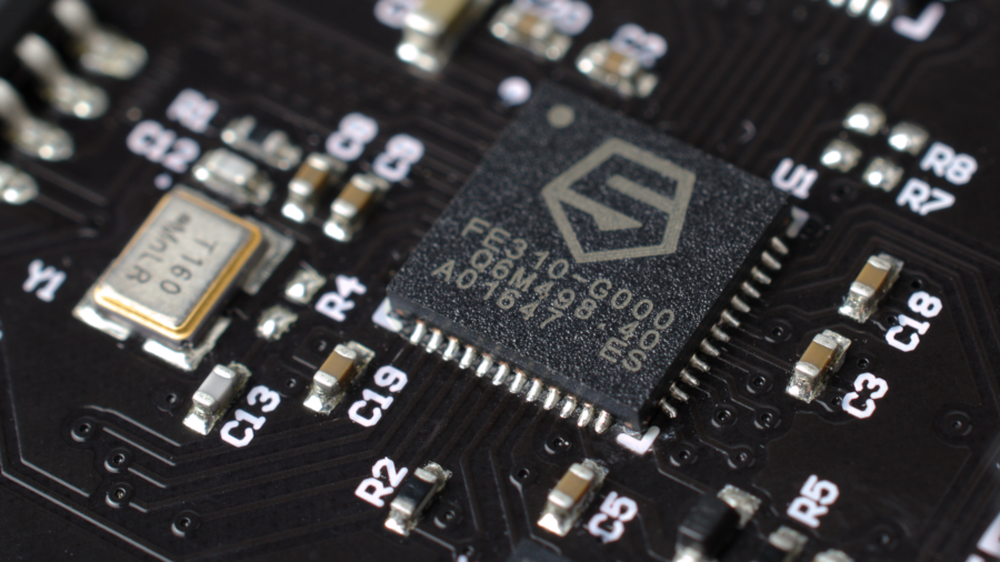

Hiện SiFive là một trong những tên tuổi đi đầu về thiết kế nhân CPU dùng kiến trúc RISC-V và cũng là hãng đi đầu trong việc quảng bá kiến trúc tập lệnh này. Còn đối với Microchip, một trong các lý do giúp họ được NASA lựa chọn vì nổi tiếng với việc tạo ra các thiết bị có khả năng chống bức xạ - một yếu tố quan trọng cho các nhiệm vụ ngoài không gian.

So với các kiến trúc như x86 trong CPU của Intel và AMD, hoặc trong các thiết kế chip của hãng ARM, kiến trúc tập lệnh RISC-V có tuổi đời khá non trẻ. Mới được khởi xướng từ năm 2010 tại trường Đại học California, RISC-V là một kiến trúc tập lệnh mã nguồn mở miễn phí, được xây dựng dựa trên các nguyên tắc về hiệu quả năng lượng nhưng không phải trả tiền như bản quyền cho những công ty như ARM.

Nhờ đó, RISC-V được kỳ vọng sẽ giúp giảm chi phí thiết kế bán dẫn do không phải chi trả chi phí bản quyền mỗi khi chúng được tích hợp trong các con chip. Từ đó, nó sẽ giúp giảm chi phí phần cứng và phần mềm nhờ sự cạnh tranh giữa những nhà cung cấp và khả năng tái sử dụng nhiều lần. Chính vì vậy, RISC-V được cho có tiềm năng trở thành đối thủ của nền tảng ARM trong tương lai.

Tuy nhiên, với tuổi đời còn non trẻ hiện tại các bộ xử lý RISC-V vẫn còn quá hiếm hoi so với hàng tỷ bộ xử lý sử dụng nền ARM hoặc x86 hiện nay. Tuy nhiên, kể từ khi hãng Huawei bị chính phủ Mỹ trừng phạt và không thể mua được các con chip có nguồn gốc công nghệ Mỹ, kiến trúc RISC-V bắt đầu nhận được sự chú ý do không vướng phải các giới hạn và rào cản về bản quyền công nghệ như các bộ xử lý hiện tại.

Điều đó giải thích lý do vì sao Trung Quốc hiện đang tập trung nghiên cứu phát triển các bộ xử lý nền RISC-V để giảm thiểu sự phụ thuộc vào các công ty bán dẫn phương Tây. Ngay cả Intel cũng đang quan tâm đến kiến trúc tập lệnh này khi e ngại rằng, các bộ xử lý x86 của họ không thể cạnh tranh nổi hiệu quả năng lượng của RISC-V trong dài hạn.

Theo số liệu của hãng Deloitte, số lượng nhân RISC-V đang lưu hành trên thế giới hiện tăng gấp đôi sau mỗi hai năm, nhờ một phần không nhỏ nỗ lực truyền bá tập lệnh này của hãng SiFive, vốn được sáng lập bởi những người đã tạo nên khái niệm Kiến trúc tập lệnh ISA.

Với kiến trúc được xây dựng dựa trên các nguyên tắc về hiệu quả năng lượng cũng như khả năng tùy chỉnh mạnh mẽ, dễ hiểu vì sao NASA lại lựa chọn kiến trúc RISC-V này cho các bộ xử lý của mình trong tương lai.

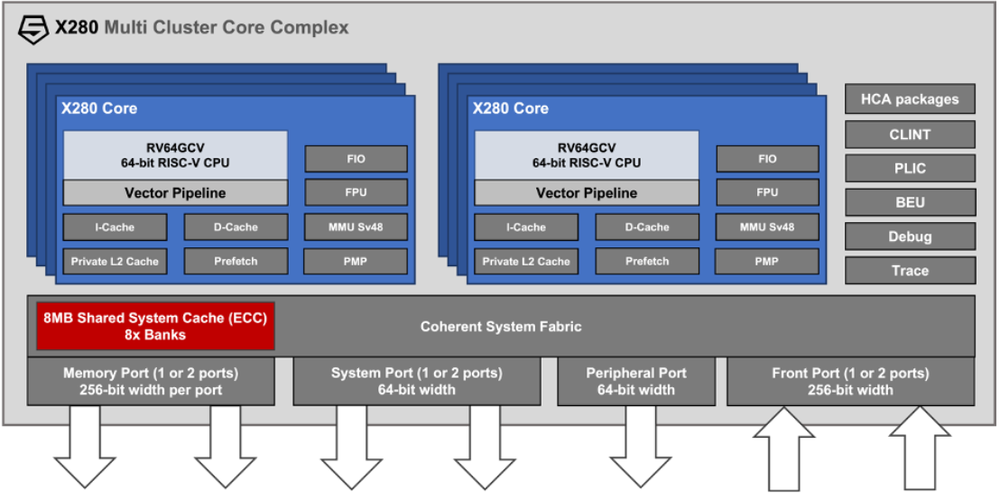

Kiến trúc trong nhân X280 của SiFive

Đại diện của SiFive cho biết việc NASA lựa chọn bộ xử lý dùng kiến trúc RISC-V cho thấy hiệu quả của phong trào mà họ đang thúc đẩy. Với việc xuất hiện trong các máy tính sẽ bay vào không gian của NASA, SiFive cùng các công ty chip RISC-V khác sẽ được hưởng lợi trong nhiều thập kỷ tới khi nền tảng này có thể được xem như sự thay thế cho các đối thủ.

Theo tuyên bố của SiFive, bộ xử lý HPSC của NASA sẽ có 12 nhân, với 4 nhân RISC-V đa dụng và 8 nhân xử lý vector chuyên dụng X280, nhằm mở rộng khả năng chạy các đoạn mã ứng dụng cho bộ xử lý RISC-V.

Niki Werkheiser, giám đốc Công nghệ Hoàn thiện của NASA, cho biết: "Bộ xử lý tiên tiến cho tàu vũ trụ này sẽ có tác động to lớn đến các sứ mệnh không gian trong tương lai và thậm chí cho các công nghệ trên Trái Đất."

"Nỗ lực này sẽ tăng cường khả năng hiện tại của tàu vũ trụ và mang lại các tính năng mới và cuối cùng có thể được sử dụng trong hầu như mọi nhiệm vụ không gian trong tương lai, tất cả đều được hưởng lợi từ khả năng tính toán bay mạnh mẽ hơn."